|

22.01.2007 13:23

просмотров: сегодня 2, всего 1022

автор новости: VMir |

| связанные темы: HP; технологии |

На прошлой неделе из штаб-квартиры компьютерного лидера

Hewlett-Packard Co. в Пало-Альто (Калифорния) пришли новости о результатах последних научных разработок, определяющих стратегию компании по совершенствованию микрочипов на ближайшие 10-15 лет. Эта стратегия названа альтернативной.

Применение новой технологии FPNI

позволит повысить плотность чипа

в 8 раз, не уменьшая размер транзисторов

Последние несколько десятилетий основным направлением совершенствования микросхем было увеличение плотности размещения транзисторов благодаря уменьшению их размера. Элементы современных транзисторов уже имеют размер нескольких десятков нанометров – примерно в 1000 раз тоньше человеческого волоса. Становится очевидным, что это направление исчерпало свои возможности вплотную приблизившись к технологическим пределам.

Необходимо отметить, что около 80% от общего числа транзисторов микросхемы работают не над решением задач, а на обеспечение маршрутизации. То есть пространство современной микросхемы используется всего на 20-30%. Этим резервом и намерена воспользоваться НР, применяя прогрессивную технологию на основе программируемых вентильных матриц — FPGA (Field Programmable Gate Array), а также собственную технологию Crossbar Latch («поперечный затвор»). Словосочетание FPGA еще переводится как программируемая логическая матрица, что поясняет принцип действия технологии, согласно которой связи между отдельными элементами микросхемы (или микросхемами) не являются прошитыми навсегда, их можно перепрограммировать с учетом текущих задач при помощи программы-компилятора.

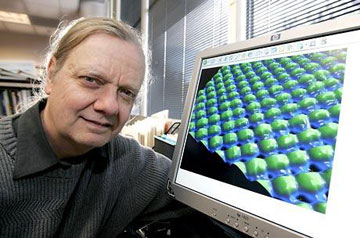

Свою технологию НР назвала FPNI (Field-Programmable Nanowire Interconnect). Согласно ей на слой CMOS (КМОП — комплементарных металло-оксидных полупроводников) наносится наноматрица Crossbar Latch, представляющая собой решетку из нанопровода с затворами-переключателями. Функции внутри микросхемы распределены следующим образом: транзисторы CMOS выполняют основную задачу — логические операции, нанорешетка осуществляет связь – передачу сигналов между ними. Вот в этом-то и альтернатива – размеры транзисторов не меняются, а плотность чипа увеличивается в 8 раз. Вдобавок снижается энергопотребление.

Специалисты компании продемонстрировали две модели прототипа чипов, которые планируется выпускать в 2010 и 2020 годах соответственно.

Первая представляет сочетание 15 нм нанорешетки Crossbar Latch переключателей с 45 нм CMOS матрицей.

Если привести к традиционному пути развития – это скачок через три поколения совершенствования кремниевых чипов без изменения размеров транзисторов.

Вторая модель основана на 4,5 нм Crossbar Latch архитектуре в сочетании с 45 нм CMOS-матрицей. При всех равных показателях размеры этого «гибрида» в 25 раз меньше аналога, изготовленного по технологии FPGA.

Специалисты НР приводят еще два аргумента в пользу внедрения демонстрируемых чипов. Во-первых, их производство не потребует коренных изменений в технологии изготовления и оборудовании. Во-вторых, чипы сверхстойки к повреждениям. Миниатюрные размеры нанопроводов и затворов-переключателей предполагают технологически высокий уровень дефектов. Благодаря новой архитектуре поврежденные участки можно безболезненно обходить. На экспериментальном образце FPNI чипа случайным образом было повреждено 20% общей емкости нанорешетки, что никак не повлияло на работоспособность и производительность микросхемы.

- « оценка: 4.5 (2 чел.) » +

|

Устанавливайте линк на Ладошки на своих сайтах, изучайте коммерческую информацию,

посещайте разделы сайта (форум, чат, новости, файлы, прочие). Оцените эту новость и оставьте свой комментарий ниже на странице.